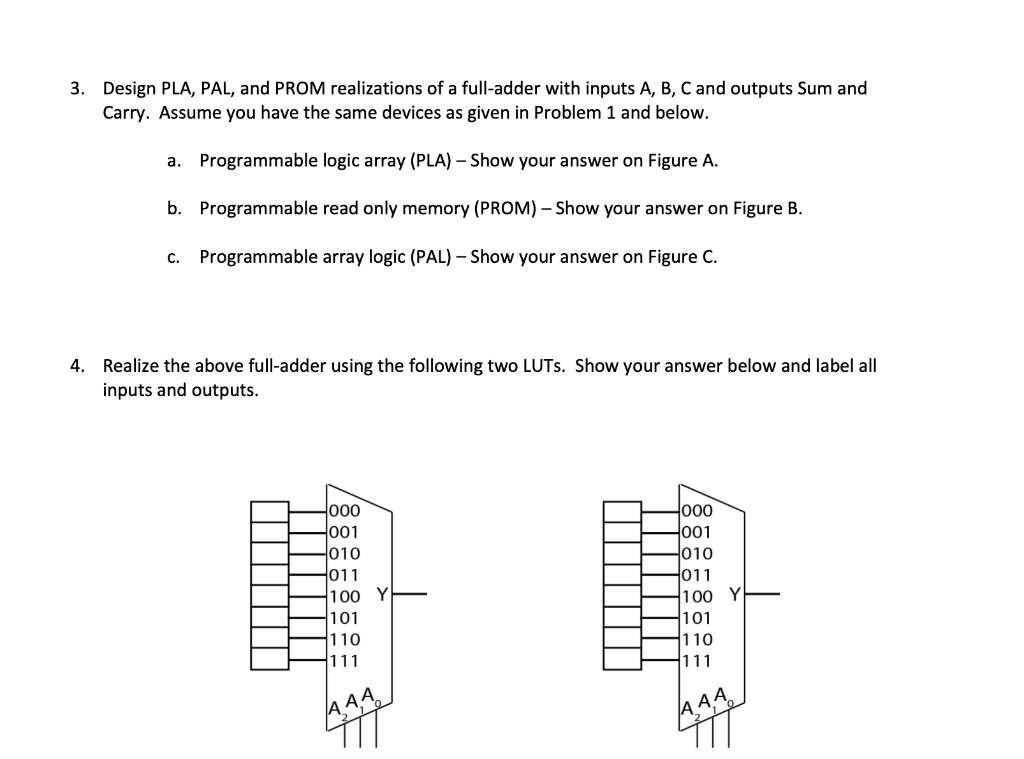

Design PLA PAL and PROM realizations of a full-adder with inputs A B C and outputs Sum and Carry. Next the full adder FA2 uses this carry bit C2 to add with the input bits A2 and B2 to generate the sum.

Solved 3 Design Pla Pal And Prom Realizations Of A Chegg Com

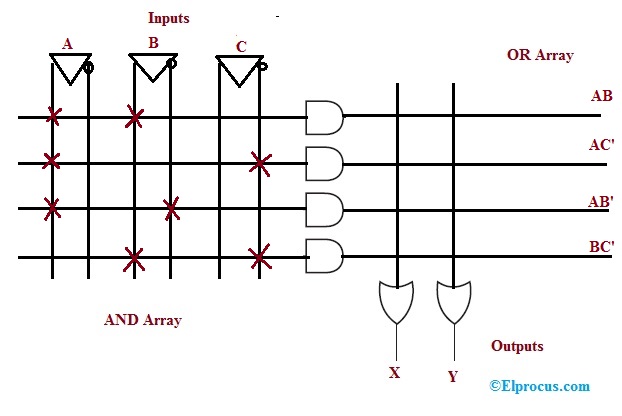

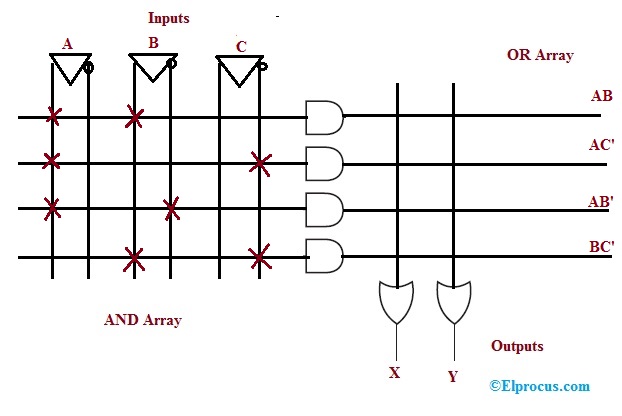

The block diagram of PAL is shown in the following figure.

. Field Programmable Gate Array FPGA Consists of lookup tables multiplexers gates and flip-flops. To verify the operation of the above design initially assume that X0 and Q1Q2Q3000. Download as PPT PDF TXT or read online from Scribd.

Assume you have the same devices as given in Problem 1 and below. 1 Answer Write a note on Full Adder. PLDADDERPALhow to implement full adder using PAL In this video lecture i have explained how we can design full adder using PAL.

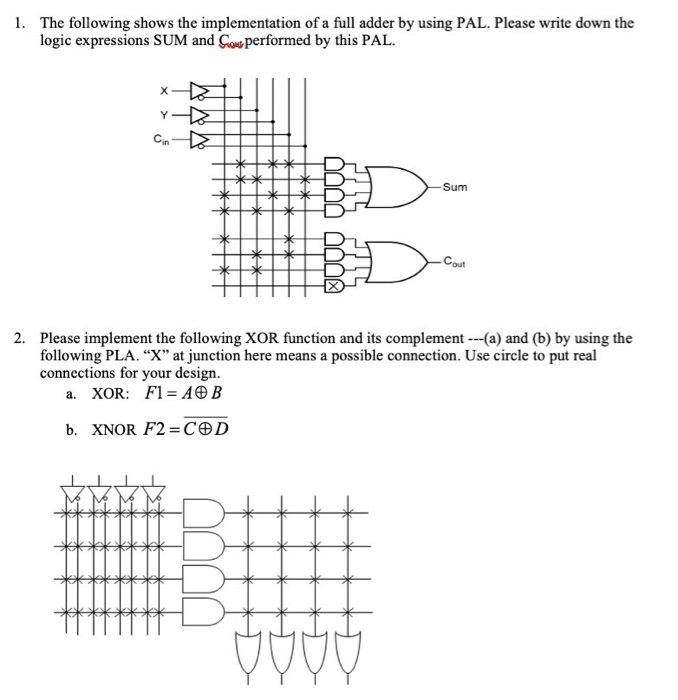

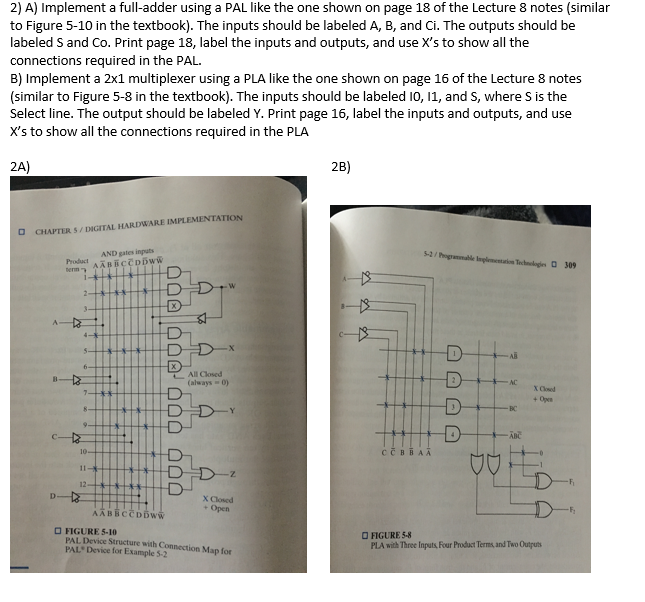

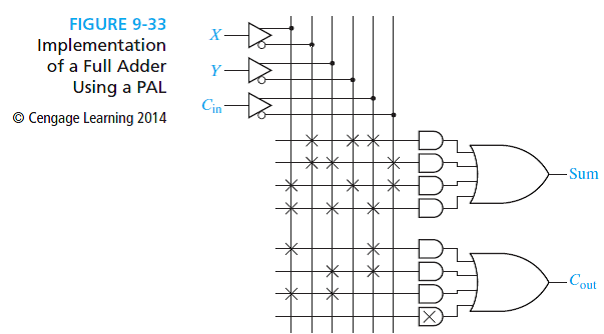

Written 35 years ago by vedantchikhale 440. A Implement a full-adder using a PAL like the one shown on page 18 of the Lecture 8 notes similar to Figure 5-10 in the textbook. Programmable Array Logic PAL is a commonly used programmable logic device PLD.

Includes AND-OR array PAL or PLA and flip-flops Complex Programmable Logic Device CPLD Collection of PLDs on a single integrated circuit and IO blocks. Design full adder using pla and pal Purity motivated nail art with white heart designs over the nail recommendations basic however classy. Save Save Lecture 1 - Multiplexer ROMPLA and PAL For Later.

ADD COMMENT FOLLOW SHARE EDIT. 100 6 100 found this document useful 6 votes 22K views 47 pages. The inputs should be labeled A B and Ci.

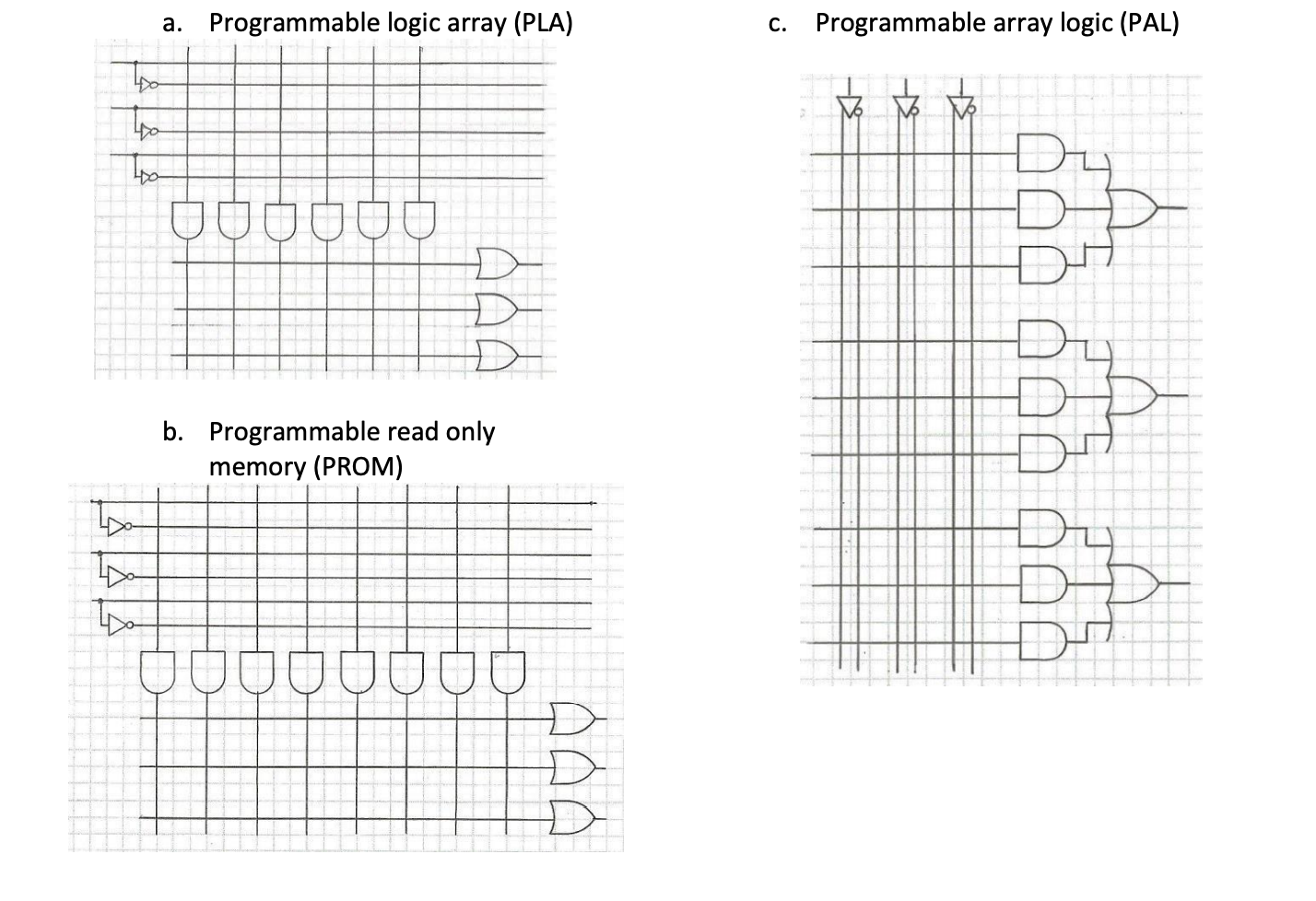

IMPLEMENTING FULL ADDER WITH PAL Logic Equations for Full Adder Sum XYC in XYC in XYC in XYC in C out XC in YC in XY 35 Segment of a Sequential PAL Q D A BQ AB Q The flip-flop output is connected to an inverting tristate buffer which is enabled when EN 1 36. Programmable logic array PLA - Show your answer on Figure A. Assume you have the same devices as given in Problem 1 and below.

PLA and PAL are types of Programmable Logic Devices PLD which are used to design combination logic together with sequential logic. 1 Answer Design Full Adder and Implement it using two half adders. FULLADDERUSING PLDIn this video i have discussed how we can implement full adder using PLAlink for 1x32 demux using 1x8 demuxhttpsyoutubenjmMv2x1Kw8Lin.

1 Answer Show that a full adder can be constructed using two half adders. PLDs have an undefined function at the time of manufacturing but they are programmed before made into use. The significant difference between the PLA and PAL is that the PLA consists of the programmable array of AND and OR gates while PAL has the programmable array of AND but a fixed array of OR gate.

It has programmable AND array and fixed OR array. Modified 25 years ago by abhishektiwari1 100. Shades of white and silver beads are preferred because they can easily match your outfit whatsoever celebration it.

1 Answer Write a note on draw back of 4bit parallel binary adder. The design with PLD CPLD or FPGA requires extensive computer-. Design Full Adder Using Pla And Pal.

The advantage of PAL is that we can generate only the required product terms of Boolean function instead of generating all the min terms by using programmable AND gates. As shown in the figure firstly the full adder FA1 adds A1 and B1 along with the carry C1 to generate the sum S1 the first bit of the output sum and the carry C2 which is connected to the next adder in chain. Explain Full Adder circuit using PLA having three inputs 8 product terms and two outputs.

Prompld problems 1. Programmable read only memory PROM - Show your answer on Figure B. Programmable logic array PLA - Show your answer on Figure A.

Consider the truth table of full-adder Consider expression for outputs S and Co 𝑆 1 2 4 7 and 𝐶 3 5 6 7 i Note that PROM has a fixed AND plane usually implemented by using a decoder of suitable size and a. The expected value of the distance between a and b in T ie the number of edges in the unique path between a and b is rounded off to 2 decimal places 1 Answer Realize half adder using NAND gates only 1 Answer Implement a half adder using pla. Section 641 - Design Procedure with PLA.

Print page 18 label the inputs and outputs and use Xs to show all the connections required in the PAL. The outputs should be labeled S and Co. This table can be realized by using PLA with four inputs seven product terms and four outputs.

PLA is basically a type of programmable logic device used to build a reconfigurable digital circuit. It is never necessary to minimize the expressions prior to obtaining the realization with a ROM. Implement a full-adder using a PAL like the one shown on page 18 of the Lecture 8 notes similar to Figure 5-10 in the textbook.

2 Answer What is full stack. DSD and HDL Simulation Assignment Questions Problem Give the implementation of full-adder using i PROM ii PAL Solution. The inputs should be labeled A B and Ci.

Explain the Implementation of Full adder using PLA. C n-full adders are needed to implement n-bit parallel adder and only 1 full adder is needed to implement serial adder. Programmable Logic Array PLA is a fixed architecture logic device with programmable AND gates followed by programmable OR gates.

Design PLA PAL and PROM realizations of a full-adder with inputs A B C and outputs Sum and Carry. Programmable Array Logic PAL PAL is a programmable logic device that has Programmable AND array fixed OR array. Print page 18 label the inputs and outputs and use Xs to show all the connections required in the PAL.

The outputs should be labeled S and Co. In the case of ROM-based design we have seen that since all the minterms are generated in a ROM the realization of a set of Boolean functions is based on minterms canonical expressions. B PAL contains a fixed AND array and a programmable OR array c PROM contains a fixed AND array and a programmable OR array d PLA contains a programmable AND array and a pgrogrammable OR array Answers With Solutions 1.

PALs only limitation is number of AND gates. Programmable array logic PAL - Show your. 1 Answer Rewrite the following code in Python after removing all syntax errors.

This selects rows 0- and 0 -0 in the table so Z0 and D1D2D3100. Because only the AND array is programmable it is easier to use but not flexible as compared to Programmable Logic Array PLA. Flag for inappropriate content.

The PLA table which corresponds to these equations is given in the table above. Programming Array Logic. Written 34 years ago by vedantchikhale 440 modified 34 years ago.

Solved 3 Design Pla Pal And Prom Realizations Of A Chegg Com

Solved 1 The Following Shows The Implementation Of A Full Chegg Com

What Are Pal And Pla Logic Design Example And Differences

Multiplexers Decoders And Programmable Logic Devices Ppt Video Online Download

Explain Full Adder Circuit Using Pla Having Three Inputs 8 Product Terms And Two Outputs

Solved Implement A Full Adder Using A Pal Like The One Shown Chegg Com

Solved Show How To Implement A Full Subtracter Using A Pal See F Chegg Com

0 comments

Post a Comment